Darklife Research Builds RISC-V Processor Entirely in Rust, Runs Rust Code

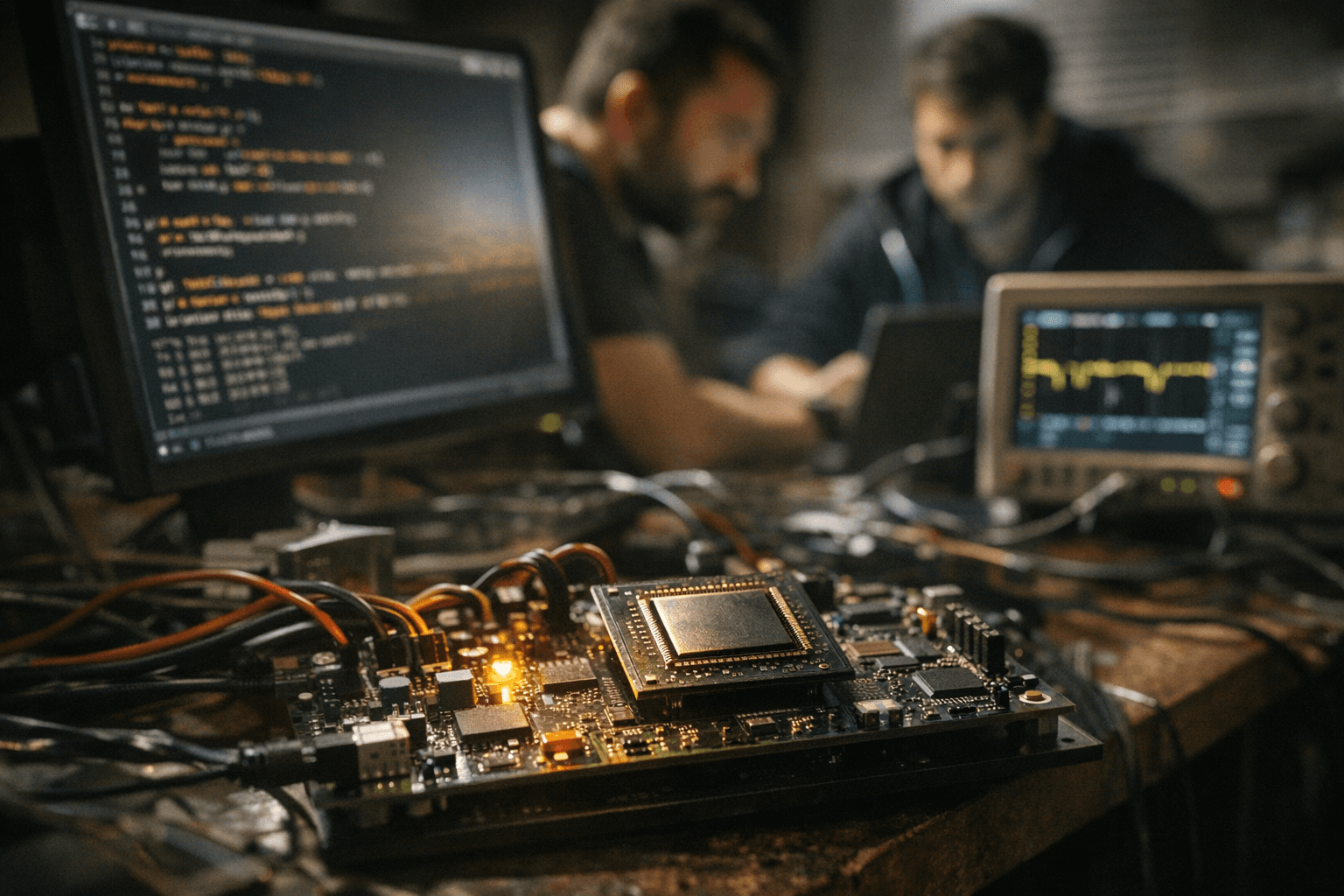

Darklife Research's RUST-V is a RISC-V processor built entirely in Rust that can run Rust code and, in an ironic twist, produce segmentation faults.

The processor that undermines Rust's most celebrated promise can still run Rust code just fine. Darklife Research's RUST-V is a RISC-V softcore implemented entirely in Rust, and among its verified capabilities is the ability to produce segmentation faults, the exact class of memory-safety error that Rust was engineered to make impossible at the language level.

The irony is architectural, not accidental. Rust's borrow checker enforces memory safety in software, but RUST-V drops below that abstraction layer and makes Rust the hardware substrate itself. When Rust becomes the silicon (or in this case, the FPGA logic), the language's compile-time guarantees no longer apply in the same way. Hardware-level behavior follows hardware rules.

Darklife Research has been in this territory before. The same team built DarkRISCV, an open-source RISC-V CPU softcore written in Verilog, reportedly completed in a single sitting on 19 Aug 2018 between 2am and 8am. That project implements UC Berkeley's RISC-V RV32E and RV32I user-space instruction sets and has been validated on real Xilinx hardware, including Spartan-3 and Spartan-6 FPGAs. DarkRISCV has since accumulated over 2,500 GitHub stars. RUST-V is the same team's natural next move: replace Verilog with Rust as the hardware description medium.

That replacement puts Darklife Research inside a fast-moving field. Samit Basu's RustHDL crate lets engineers write FPGA firmware in Rust by compiling a subset of the language to Verilog. Basu followed it with RHDL, presented at Cornell University's LATTE workshop, which takes a zero-cost abstraction approach and benchmarks at roughly one to two orders of magnitude faster than RustHDL. The direction across both projects is the same: Verilog and VHDL are aging tools, and Rust's type system offers something neither of them can.

The Rust-plus-RISC-V pairing already has deep roots in the community. Takahiro Okumura's riscv-rust is a RISC-V processor emulator compiled to WebAssembly that runs Linux and xv6 directly in a browser. The rust-embedded working group's riscv crate has surpassed 5.7 million all-time downloads on crates.io, providing low-level register access for embedded developers. The line RUST-V draws between itself and those projects is precise: they run Rust on RISC-V, or emulate RISC-V in Rust. RUST-V implements the processor logic itself in Rust.

RISC-V's royalty-free instruction set, born at UC Berkeley and now stewarded by the global nonprofit RISC-V International, has always attracted hobbyist and research processor work as an open alternative to ARM and x86. Darklife Research joined that ecosystem early with DarkRISCV. RUST-V pushes the project into new ground: a working processor core where Rust is not the target platform but the construction material, segfaults and all.

Know something we missed? Have a correction or additional information?

Submit a Tip